### ISO/IEC 24739-2

Edition 1.0 2009-11

# INTERNATIONAL STANDARD

Information technology – AT attachment with packet interface-7 – Part 2: Parallel transport protocols and physical interconnect (ATA/ATAPI-7)

INTERNATIONAL ELECTROTECHNICAL COMMISSION

PRICE CODE

ISBN 2-8318-1071-0

### CONTENTS

| FOF | REWO   | DRD       |                                                                      | 10  |

|-----|--------|-----------|----------------------------------------------------------------------|-----|

| INT | RODU   | JCTION    |                                                                      | .11 |

| 1   | Scop   | e         |                                                                      | 12  |

| 2   | Norm   | ative re  | ferences                                                             | .12 |

| 3   | Term   | s, defini | itions, abbreviations, conventions and keywords                      | 12  |

|     | 3.1    | Terms,    | definitions and abbreviations                                        | 12  |

|     | 3.2    | Abbrev    | iations                                                              | 21  |

|     | 3.3    | Conver    | ntions                                                               | 22  |

|     |        | 3.3.1     | General                                                              | 22  |

|     |        | 3.3.2     | Precedence                                                           | 22  |

|     |        | 3.3.3     | Lists                                                                |     |

|     |        | 3.3.4     | Keywords                                                             | 22  |

|     |        | 3.3.5     | Numbering                                                            | 23  |

|     |        | 3.3.6     | Signal conventions                                                   |     |

|     |        | 3.3.7     | Bit conventions                                                      |     |

|     |        | 3.3.8     | State diagram conventions                                            |     |

|     |        | 3.3.9     | Timing conventions                                                   |     |

|     |        |           | Byte ordering for data transfers                                     |     |

|     |        |           | Byte, word and DWORD relationships                                   | 28  |

|     | 3.4    |           | nship of this part of ISO/IEC 24739 to ISO/IEC 24739-1 and C 24739-3 | 28  |

| 4   | Gene   |           | ational requirements                                                 |     |

| 5   | I/O re | egister d | lescriptions                                                         | 28  |

| 6   |        | _         | escriptions                                                          |     |

| 7   | Paral  | lel inter | face physical and electrical requirements                            | 29  |

|     | 7.1    | Cable     | configuration                                                        | 29  |

|     | 7.2    | Electric  | cal characteristics                                                  | 29  |

|     |        | 7.2.1     | General                                                              | 29  |

|     |        | 7.2.2     | AC characteristics measurement techniques                            | 31  |

|     |        | 7.2.3     | Driver types and required termination                                | 32  |

|     |        | 7.2.4     | Electrical characteristics for Ultra DMA                             | 32  |

|     | 7.3    | Connec    | ctors and cable asemblies                                            | 35  |

|     |        | 7.3.1     | General                                                              | 35  |

|     |        | 7.3.2     | 40-pin connector                                                     | 35  |

|     |        | 7.3.3     | 4-pin power connector                                                | 44  |

|     |        | 7.3.4     | Unitized connectors                                                  | 46  |

|     |        | 7.3.5     | 50-pin 65 mm (2.5 in) form factor style connector                    | 48  |

|     |        | 7.3.6     | 68-pin PCMCIA connector                                              | 51  |

|     |        | 7.3.7     | 48 mm (1.8 in) 3.3 V parallel connector                              |     |

|     | 7.4    | Physica   | al form factors                                                      | 57  |

|     |        | 7.4.1     | 95 mm (3.5 in) form factor                                           |     |

|     |        | 7.4.2     | 65 mm (2.5 in) form factor                                           |     |

|     |        | 7.4.3     | 48 mm (1.8 in) PCMCIA form factor                                    |     |

|     |        | 7.4.4     | 48 mm (1.8 in) 5 V parallel form factor                              |     |

|     |        | 7.4.5     | 48 mm (1.8 in) 3.3 V parallel form factor                            |     |

|     |        | 7.4.6     | 130 mm (5.25 in) form factor                                         | 69  |

| 8  | Paral      | llel inter | face signal assignments and descriptions                                         | 73         |

|----|------------|------------|----------------------------------------------------------------------------------|------------|

|    | 8.1        | Signal     | summary                                                                          | 73         |

|    | 8.2        | Signal     | descriptions                                                                     | 74         |

|    |            | 8.2.1      | CS(1:0)- (Chip select)                                                           |            |

|    |            | 8.2.2      | DA(2:0) (Device address)                                                         | 74         |

|    |            | 8.2.3      | DASP- (device active, device 1 present)                                          | 74         |

|    |            | 8.2.4      | DD(15:0) (Device data)                                                           |            |

|    |            | 8.2.5      | DIOR-:HDMARDY-:HSTROBE (Device I/O read:Ultra DMA ready:Ultra DMA data strobe)   |            |

|    |            | 8.2.6      | DIOW-:STOP (Device I/O write:Stop Ultra DMA burst)                               |            |

|    |            | 8.2.7      | DMACK- (DMA acknowledge)                                                         |            |

|    |            | 8.2.8      | DMARQ (DMA request)                                                              |            |

|    |            | 8.2.9      | INTRQ (Device interrupt)                                                         |            |

|    |            | 8.2.10     | IORDY:DDMARDY-:DSTROBE (I/O channel ready:Ultra DMA ready:Ultra DMA data strobe) |            |

|    |            | 8.2.11     | PDIAG-:CBLID- (passed diagnostics: cable assembly type identifier)               |            |

|    |            |            | RESET- (Hardware reset)                                                          |            |

|    |            |            | CSEL (cable select)                                                              |            |

| 9  |            | llel inter | face general operational requirements of the physical, data link and ers         |            |

|    |            | -          |                                                                                  |            |

|    | 9.1<br>9.2 |            | pts                                                                              |            |

|    | 9.2        |            | ord DMA  DMA feature set                                                         |            |

|    | 9.3        | 9.3.1      | Overview                                                                         |            |

|    |            | 9.3.1      | Phases of operation                                                              |            |

|    | 9.4        |            | etermination of cable type by detecting CBLID-                                   |            |

| 10 |            |            | face register addressing                                                         |            |

|    |            |            | face transport protocol                                                          |            |

| 11 |            |            |                                                                                  |            |

|    | 11.1       |            | eral                                                                             |            |

|    | 11.2       |            | er-on and hardware reset protocol                                                |            |

|    | 11.3       |            | vare reset protocol                                                              |            |

|    | 11.4       |            | idle protocol                                                                    |            |

|    | 11.5       |            | data command protocol                                                            |            |

|    | 11.6       |            | data-in command protocol                                                         |            |

|    | 11.7       |            | data-out command protocol                                                        |            |

|    | 11.8       |            | command protocol                                                                 |            |

|    | 11.9       |            | KET command protocol                                                             |            |

|    | 11.10      |            | D/WRITE DMA QUEUED command protocol                                              |            |

|    | 11.11      |            | CUTE DEVICE DIAGNOSTIC command protocol                                          |            |

|    | 11.12      |            | ICE RESET command protocol                                                       |            |

|    | 11.13      |            | DMA data-in commands                                                             |            |

|    |            |            | 3.1 Initiating an Ultra DMA data-in burst                                        |            |

|    |            |            | 3.2 The data-in transfer                                                         |            |

|    | 11 1       |            | 3.3 Pausing an Ultra DMA data-in burst                                           |            |

|    | 11.14      |            |                                                                                  |            |

|    |            |            | 4.1 Initiating an Ultra DMA data-out burst                                       |            |

|    |            |            | 4.3 Pausing an Ultra DMA data-out burst                                          |            |

|    |            |            | 4.5 Pausing an Oilla DMA data-out burst                                          | 155<br>156 |

| 11.15 Ultra DMA CRC rules                                                            | 157 |

|--------------------------------------------------------------------------------------|-----|

| 12 Parallel interface timing                                                         | 159 |

| 12.1 Deskewing                                                                       | 159 |

| 12.2 Transfer timing                                                                 | 159 |

| 12.2.1 General                                                                       | 159 |

| 12.2.2 Register transfers                                                            | 159 |

| 12.2.3 PIO data transfers                                                            |     |

| 12.2.4 Multiword DMA data transfer                                                   |     |

| 12.2.5 Ultra DMA data transfer                                                       |     |

| 13 Serial interface overview                                                         |     |

| 14 Serial interface physical layer                                                   |     |

| 15 Serial interface link layer                                                       | 182 |

| 16 Serial interface transport layer                                                  | 182 |

| 17 Serial interface device command layer                                             | 182 |

| 18 Host command layer                                                                | 182 |

| 19 Serial interface host adapter register interface                                  | 182 |

| 20 Serial interface error handling                                                   | 182 |

| Annex A (informative) Command Set summary                                            | 183 |

| Annex B (informative) Design and programming considertions for large physical sector |     |

| sizes                                                                                | 184 |

| Annex C (informative) Device determination of cable type                             |     |

| C.1 Overview                                                                         | 185 |

| C.2 Sequence for device detection of installed capacitor                             | 185 |

| C.3 Using the combination of methods for detecting cable type                        | 187 |

| Annex D (informative) Signal integrity and UDMA guide                                | 188 |

| D.1 General                                                                          | 188 |

| D.2 Issues                                                                           | 188 |

| D.2.1 General                                                                        | 188 |

| D.2.2 Timing                                                                         | 189 |

| D.2.3 Crosstalk                                                                      | 195 |

| D.2.4 Ground/power bounce                                                            | 207 |

| D.2.5 Ringing and data settling time (DST) for the 40-conductor cable assembly       | 208 |

| D.3 System guidelines for Ultra DMA                                                  | 214 |

| D.3.1 General                                                                        |     |

| D.3.2 System capacitance                                                             |     |

| D.3.3 Pull-up and pull-down resistors                                                |     |

| D.3.4 Cables and connectors                                                          |     |

| D.3.5 Host PCB and IC design                                                         |     |

| D.3.6 Sender and recipient component I/Os                                            |     |

|                                                                                      |     |

| D.4.1 General                                                                        |     |

| D.4.2 DC characteristics  D.4.3 AC characteristics                                   |     |

| D.5 Ultra DMA timing and protocol                                                    |     |

| D.5.1 Ultra DMA timing assumptions                                                   |     |

| D.5.2 Ultra DMA timing parameters                                                    |     |

| D.5.3 Ultra DMA protocol considerations                                              |     |

| D.6 Cable detection                                                     | 238 |

|-------------------------------------------------------------------------|-----|

| D.6.1 General                                                           | 238 |

| D.6.2 80-conductor cable assembly electrical feature                    | 238 |

| D.6.3 Host determination of cable assembly type                         |     |

| D.6.4 Device determination of cable assembly type                       |     |

| Annex E (informative) Register selection address summary                |     |

| Annex F (informative) Sample Code for CRC and Scrambling                |     |

| Annex G (informative) FIS type field value selection                    |     |

| Annex H (informative) Physical Layer Implementation Examples            |     |

| Annex I (informative) Command processing Example                        |     |

| Bibliography                                                            | 248 |

| Figure 1 – ATA document relationships                                   |     |

| Figure 2 – State diagram convention                                     |     |

| Figure 3 – Byte, word and DWORD relationships                           | 28  |

| Figure 4 – Ultra DMA termination with pull-up or pull-down              | 34  |

| Figure 5 – Host or device 40-pin I/O header                             | 36  |

| Figure 6 – 40-pin I/O cable connector                                   |     |

| Figure 7 – 40-pin I/O header mounting                                   | 38  |

| Figure 8 – 40-conductor cable configuration                             | 39  |

| Figure 9 – 80-conductor ribbon cable                                    | 40  |

| Figure 10 – 80-conductor cable configuration                            | 41  |

| Figure 11 – Connector labeling for even or odd conductor grounding      | 44  |

| Figure 12 – Device 4-pin power header                                   | 44  |

| Figure 13 – 4-pin power cable connector                                 | 45  |

| Figure 14 – Unitized connector                                          | 47  |

| Figure 15 – Unitized connector                                          | 48  |

| Figure 16 – 50-pin 65 mm (2.5 in) form factor style connector           | 49  |

| Figure 17 – 48 mm (1.8 in) 3.3 V parallel connector                     | 54  |

| Figure 18 – 48 mm (1.8 in) 3.3 V parallel host connector                | 55  |

| Figure 19 – 95 mm (3.5 in) form factor                                  | 58  |

| Figure 20 – 65 mm (2.5 in) form factor                                  | 60  |

| Figure 21 – 65 mm (2.5 in) form factor mounting holes                   | 62  |

| Figure 22 – 65 mm (2.5 in) form factor connector location               | 63  |

| Figure 23 – 48 mm (1.8 in) 5 V parallel form factor                     | 65  |

| Figure 24 – 48 mm (1.8 in) 5 V parallel form factor connector location  | 67  |

| Figure 25 – 48 mm (1.8 in) 3.3 V parallel form factor                   | 68  |

| Figure 26 – 130 mm (5.25 in) HDD form factor                            | 70  |

| Figure 27 – 130 mm (5.25 in) CD-ROM form factor                         | 71  |

| Figure 28 – 130 mm (5.25 in) CD-ROM connector location                  | 72  |

| Figure 29 – Cable select example                                        | 78  |

| Figure 30 – Alternate cable select example                              | 79  |

| Figure 31 – Example configuration of a system with a 40-conductor cable | 84  |

| Figure 32 – Example configuration of a system where the host detects a 40-conductor cable  | 84  |

|--------------------------------------------------------------------------------------------|-----|

| Figure 33 – Example configuration of a system where the host detects an 80-conductor cable | 85  |

| Figure 34 – Overall host protocol state sequence                                           |     |

| Figure 35 – Overall device protocol state sequence                                         |     |

| Figure 36 – Host power-on or hardware reset state diagram                                  |     |

| Figure 37 – Device power-on or hardware reset state diagram                                |     |

| Figure 38 – Host software reset state diagram                                              |     |

| Figure 39 – Device 0 software reset state diagram                                          |     |

| Figure 40 – Device 1 software reset state diagram                                          |     |

| Figure 41 – Host bus idle state diagram                                                    |     |

| Figure 42 – Additional Host bus idle state diagram with overlap or overlap and queuing     |     |

| Figure 43 – Device bus idle state diagram                                                  |     |

| Figure 44 – Additional device bus idle state diagram with overlap or overlap and           |     |

| queuing                                                                                    |     |

| Figure 45 – Host non-data state diagram                                                    |     |

| Figure 46 – Device non-data state diagram                                                  |     |

| Figure 47 – Host PIO data-in state diagram                                                 |     |

| Figure 48 – Device PIO data-in state diagram                                               |     |

| Figure 49 – Host PIO data-out state diagram                                                |     |

| Figure 50 – Device PIO data-out state diagram                                              |     |

| Figure 51 – Host DMA state diagram                                                         |     |

| Figure 52 – Device DMA state diagram                                                       |     |

| Figure 53 – Host PACKET non-data and PIO data command state diagram                        |     |

| Figure 54 – Device PACKET non-data and PIO data command state diagram                      |     |

| Figure 55 – Host PACKET DMA command state diagram                                          |     |

| Figure 56 – Device PACKET DMA command state diagram                                        | 139 |

| Figure 57 – Host DMA QUEUED state diagram                                                  | 142 |

| Figure 58 – Device DMA QUEUED command state diagram                                        | 144 |

| Figure 59 – Host EXECUTE DEVICE DIAGNOSTIC state diagram                                   | 146 |

| Figure 60 – Device 0 EXECUTE DEVICE DIAGNOSTIC state diagram                               | 147 |

| Figure 61 – Device 1 EXECUTE DEVICE DIAGNOSTIC command state diagram                       | 149 |

| Figure 62 – Host DEVICE RESET command state diagram                                        | 150 |

| Figure 63 – Device DEVICE RESET command state diagram                                      | 151 |

| Figure 64 – Example parallel CRC generator                                                 | 158 |

| Figure 65 – Register transfer to/from device                                               | 160 |

| Figure 66 – PIO data transfer to/from device                                               | 162 |

| Figure 67 – Initiating a multiword DMA data burst                                          | 165 |

| Figure 68 – Sustaining a multiword DMA data burst                                          | 166 |

| Figure 69 – Device terminating a Multiword DMA data burst                                  |     |

| Figure 70 – Host terminating a multiword DMA data burst                                    |     |

| Figure 71 – Initiating an Ultra DMA data-in burst                                          |     |

| Figure 72 – Sustained Ultra DMA data-in burst                                              |     |

| Figure 73 – Host pausing an Ultra DMA data-in burst                                                                                        | 174 |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 74 – Device terminating an Ultra DMA data-in burst                                                                                  | 175 |

| Figure 75 – Host terminating an Ultra DMA data-in burst                                                                                    | 176 |

| Figure 76 – Initiating an Ultra DMA data-out burst                                                                                         | 177 |

| Figure 77 – Sustained Ultra DMA data-out burst                                                                                             | 178 |

| Figure 78 – Device pausing an Ultra DMA data-out burst                                                                                     | 179 |

| Figure 79 – Host terminating an Ultra DMA data-out burst                                                                                   | 180 |

| Figure 80 – Device terminating an Ultra DMA data-out burst                                                                                 | 181 |

| Figure C.1 – Example configuration of a system where the device detects a 40-conductor cable                                               | 186 |

| Figure D.1 – A transmission line with perfect source termination                                                                           | 190 |

| Figure D.2 – Waveforms on a source-terminated bus with rise time less than $T_{prop}$                                                      | 190 |

| Figure D.3 – Waveforms on a source-terminated bus with rise time greater than $T_{\text{prop}}$                                            | 191 |

| Figure D.4 – Waveforms on a source-terminated bus with R_source less than cable $Z_0$                                                      | 192 |

| Figure D.5 – Waveforms on a source-terminated bus with R_source greater than cable $Z_0\dots$                                              | 192 |

| Figure D.6 – Typical step voltage seen in ATA systems using an 80-conductor cable (measured at drive and host connectors during read)      | 193 |

| Figure D.7 – Typical step voltage seen in ATA systems using an 80-conductor cable (measured at host and drive connectors during write)     | 194 |

| Figure D.8 – Positive crosstalk pulse during a falling edge                                                                                | 196 |

| Figure D.9 – Reverse crosstalk waveform from reflected edge                                                                                | 196 |

| Figure D.10 – Model of capacitive coupling                                                                                                 | 197 |

| Figure D.11 – Waveforms resulting from capacitive coupling (at transmitter and receiver of aggressor and victim lines)                     | 198 |

| Figure D.12 – Model of inductive coupling                                                                                                  | 199 |

| Figure D.13 – Waveforms resulting from inductive coupling (at transmitter and receiver of aggressor and victim lines)                      | 199 |

| Figure D.14 – Model of capacitive and inductive coupling                                                                                   | 200 |

| Figure D.15 – Waveforms resulting from mixed capacitive and inductive coupling (at transmitter and receiver of aggressor and victim lines) | 201 |

| Figure D.16 – Model of distributed coupling                                                                                                | 202 |

| Figure D.17 – Waveforms resulting from distributed coupling (at transmitter and receiver of aggressor and victim lines)                    | 202 |

| Figure D.18 – Model of voltage divider for connector crosstalk formed by PCB and cable                                                     | 204 |

| Figure D.19 – Waveforms showing connector crosstalk dividing between PCB and cable                                                         | 205 |

| Figure D.20 – Model of ground bounce in IC package                                                                                         | 207 |

| Figure D.21 – Waveforms resulting from ground bounce (at transmitter and receiver of aggressor and victim lines)                           | 208 |

| Figure D.22 – Simple RLC model of 40-conductor cable with all data lines switching                                                         | 209 |

| Figure D.23 – Output of simple RLC model: waveforms at source and receiving connectors                                                     | 210 |

| Figure D.24 – DST measurement for a line held low while all others are switching high (ch1 on DD3 at receiver, ch2 on DD11 at receiver)    | 210 |

| Figure D.25 – DST measurement for all lines switching (ch1 at source, ch2 at receiver)                                                     | 211 |

| Figure D 26 – Improved model of 40-conductor cable ringing with termination at IC                                                          | 211 |

| Figure D.27 – Improved model of 40-conductor cable ringing with termination at connector          | 212 |

|---------------------------------------------------------------------------------------------------|-----|

| Figure D.28 – Results of improved 40-conductor model with termination at IC versus connector      | 212 |

| Figure D.29 – Results of improved 40-conductor model with source rise time of 1 ns,5 ns and 10 ns | 213 |

| Figure D.30 – DMARDY- to final STROBE <i>t</i> <sub>RFS</sub> synchronization                     | 230 |

| Figure D.31 – STROBE and DMARDY- at sender and recipient                                          | 234 |

| Table 1 – PACKET delivered command sets                                                           |     |

| Table 2 – Byte order                                                                              | 27  |

| Table 3 – Byte order                                                                              | 27  |

| Table 4 – DC characteristics                                                                      |     |

| Table 5 – AC characteristics                                                                      | 30  |

| Table 6 – Driver types and required termination                                                   |     |

| Table 7 – Host transceiver configurations                                                         | 33  |

| Table 8 – System configuration for connection between devices and systems for all transfer modes  | 33  |

| Table 9 – Typical series termination for Ultra DMA                                                | 34  |

| Table 10 – Host or device 40-pin I/O header                                                       | 36  |

| Table 11 – 40-pin I/O cable connector                                                             | 37  |

| Table 12 – 40-pin I/O connector interface signals                                                 | 38  |

| Table 13 – 40-conductor cable configuration                                                       | 39  |

| Table 14 – 80-conductor cable electrical requirements                                             | 40  |

| Table 15 – 80-conductor ribbon cable                                                              | 40  |

| Table 16 – 80-conductor cable configuration                                                       | 41  |

| Table 17 – Signal assignments for connectors grounding even conductors                            | 42  |

| Table 18 – Signal assignments for connectors grounding odd conductors                             | 43  |

| Table 19 – Device 4-pin power header                                                              | 45  |

| Table 20 – 4-pin power cable connector                                                            | 46  |

| Table 21 – 4-pin power connector pin assignments                                                  | 46  |

| Table 22 – Unitized connector                                                                     | 47  |

| Table 23 – Unitized connector                                                                     | 48  |

| Table 24 – 50-pin connector                                                                       | 49  |

| Table 25 – Signal assignments for 50-pin 65 mm (2.5 in) form factor style connector               | 50  |

| Table 26 – Signal assignments for 68-pin connector                                                | 51  |

| Table 27 – 48 mm (1.8 in) 3.3 V parallel connector                                                | 55  |

| Table 28 – 48 mm (1.8 in) 3.3 V parallel host connector                                           | 56  |

| Table 29 – Pin assignments for the 48 mm (1.8 in) 3.3 V parallel connector                        | 57  |

| Table 30 – 95 mm (3.5 in) form factor                                                             | 58  |

| Table 31 – 65 mm (2.5 in) form factor                                                             | 61  |

| Table 32 – 65 mm (2.5 in) form factor connector location                                          |     |

| Table 33 – 48 mm (1.8 in) 5 V parallel form factor                                                |     |

| Table 34 – 48 mm (1.8 in) 5 V parallel form factor connector location                             |     |

| Table 35 – 48 mm (1.8 in) 3.3 V parallel form factor                                              |     |

| Table 36 – 130 mm (5.25 in) HDD form factor                                                           | 70  |

|-------------------------------------------------------------------------------------------------------|-----|

| Table 37 – 130 mm (5.25 in) CD-ROM form factor                                                        | 72  |

| Table 38 – Interface signal name assignments                                                          | 73  |

| Table 39 – Cable type identification                                                                  | 77  |

| Table 40 – Host detection of CBLID-                                                                   | 85  |

| Table 41 – I/O registers                                                                              | 86  |

| Table 42 – Device response to DIOW-/DIOR                                                              | 87  |

| Table 43 – Device is not selected, DMACK- is not asserted                                             | 88  |

| Table 44 – Device is selected, DMACK- is not asserted                                                 | 89  |

| Table 45 – Device is selected, DMACK- is asserted (for Multiword DMA only)                            | 90  |

| Table 46 –Device 1 is selected and Device 0 is responding for Device 1                                | 91  |

| Table 47 – Device is in Sleep mode, DEVICE RESET is not implemented, DMACK- is not asserted           | 92  |

| Table 48 – Device is in Sleep mode, DEVICE RESET is implemented, DMACK- is not asserted               | 93  |

| Table 49 – Equations for parallel generation of a CRC polynomial                                      | 159 |

| Table 50 – Register transfer to/from device                                                           | 161 |

| Table 51 – PIO data transfer to/from device                                                           | 163 |

| Table 52 – Multiword DMA data transfer                                                                | 164 |

| Table 53 – Ultra DMA data burst timing requirements                                                   | 169 |

| Table 54 – Ultra DMA data burst timing descriptions                                                   | 170 |

| Table 55 – Ultra DMA sender and recipient IC timing requirements                                      | 171 |

| Table C.1 – Device detection of installed capacitor                                                   | 186 |

| Table C.2 – Results of device based cable detection if the host does not have the capacitor installed | 186 |

| Table C.3 – Results from using both host and device cable detection methods                           | 187 |

| Table C.4 – Results for all combinations of device and host cable detection methods                   | 187 |

| Table E.1 – Register functions and selection addresses except PACKET and SERVICE commands             | 242 |

| Table E.2 – Register functions and selection addresses for PACKET and SERVICE                         |     |

| commands                                                                                              | 243 |

### INFORMATION TECHNOLOGY – AT ATTACHMENT WITH PACKET INTERFACE-7 –

## Part 2: Parallel transport protocols and physical interconnect (ATA/ATAPI-7)

#### **FOREWORD**

- 1) ISO (International Organization for Standardization) and IEC (International Electrotechnical Commission) form the specialized system for worldwide standardization. National bodies that are members of ISO or IEC participate in the development of International Standards. Their preparation is entrusted to technical committees; any ISO and IEC member body interested in the subject dealt with may participate in this preparatory work. International governmental and non-governmental organizations liaising with ISO and IEC also participate in this preparation.

- 2) In the field of information technology, ISO and IEC have established a joint technical committee, ISO/IEC JTC 1. Draft International Standards adopted by the joint technical committee are circulated to national bodies for voting. Publication as an International Standard requires approval by at least 75 % of the national bodies casting a vote.

- 3) The formal decisions or agreements of IEC and ISO on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC and ISO member bodies.

- 4) IEC, ISO and ISO/IEC publications have the form of recommendations for international use and are accepted by IEC and ISO member bodies in that sense. While all reasonable efforts are made to ensure that the technical content of IEC, ISO and ISO/IEC publications is accurate, IEC or ISO cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 5) In order to promote international uniformity, IEC and ISO member bodies undertake to apply IEC, ISO and ISO/IEC publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any ISO/IEC publication and the corresponding national or regional publication should be clearly indicated in the latter.

- 6) ISO and IEC provide no marking procedure to indicate their approval and cannot be rendered responsible for any equipment declared to be in conformity with an ISO/IEC publication.

- 7) All users should ensure that they have the latest edition of this publication.

- 8) No liability shall attach to IEC or ISO or its directors, employees, servants or agents including individual experts and members of their technical committees and IEC or ISO member bodies for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication of, use of, or reliance upon, this ISO/IEC publication or any other IEC, ISO or ISO/IEC publications.

- 9) Attention is drawn to the normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 10) Attention is drawn to the possibility that some of the elements of this International Standard may be the subject of patent rights. ISO and IEC shall not be held responsible for identifying any or all such patent rights.

International Standard ISO/IEC 24739-2 was prepared by subcommittee 25: Interconnection of information technology equipment, of ISO/IEC joint technical committee 1: Information technology.

ISO/IEC 24739-2 is to be used in conjunction with ISO/IEC 24739-1 and ISO/IEC 24739-3.

The list of all currently available parts of the ISO/IEC 24739 series, under the general title Information technology – AT attachment with packet interface-7, can be found on the IEC web site.

This International Standard has been approved by vote of the member bodies and the voting results may be obtained from the address given on the second title page.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

#### INTRODUCTION

The ISO/IEC 24739 series specifies the AT attachment interface between host systems and storage devices. It provides a common attachment interface for systems manufacturers, system integrators, software suppliers and suppliers of intelligent storage devices.

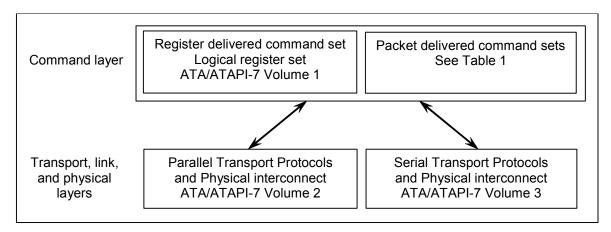

Part 1 defines the register delivered commands used by devices implementing the standard. Part 2 defines the connectors and cables for physical interconnection between host and storage device, the electrical and logical characteristics of the interconnecting signals and the protocols for the transporting of commands, data and status over the interface for the parallel interface. Part 3 defines the connectors and cables for physical interconnection between host and storage device, the electrical and logical characteristics of the interconnecting signals and the protocols for the transporting of commands, data and status over the interface for the serial interface. Figure 1 shows the relationship of these documents. For devices implementing the PACKET command feature set, additional command layer standards are listed in Table 1 and described in Clause 2.

Figure 1 – ATA document relationships

Table 1 - PACKET delivered command sets

| Standard                                                           |

|--------------------------------------------------------------------|

| SCSI Primary Commands (SPC)                                        |

| SCSI Primary Commands-2 (SPC-2)                                    |

| SCSI Primary Commands-3 (SPC-3)                                    |

| SCSI Block Commands (SBC-2)                                        |

| SCSI Stream Commands (SSC)                                         |

| Multimedia Commands (MMC)                                          |

| Multimedia Commands-2 (MMC-2)                                      |

| Multimedia Commands-3 (MMC-3)                                      |

| Multimedia Commands-4 (MMC-4)                                      |

| ATAPI for Removable Media (SFF8070I)                               |

| ATA Packet Interface (ATAPI) for Streaming Tape QIC-157 revision D |

This standard maintains compatibility with the AT Attachment with Packet Interface-6 standard (ATA/ATAPI-6) and while providing additional functions, is not intended to require changes to presently installed devices or existing software.

### INFORMATION TECHNOLOGY – AT ATTACHMENT WITH PACKET INTERFACE-7 –

## Part 2: Parallel transport protocols and physical interconnect (ATA/ATAPI-7)

#### 1 Scope

This part of ISO/IEC 24739 specifies the AT Attachment Interface between host systems and storage devices. It provides a common attachment interface for systems manufacturers, system integrators, software suppliers and suppliers of intelligent storage devices.

#### 2 Normative references

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document, including any amendments, applies.

The provisions of the referenced specifications other than ISO/IEC, IEC, ISO and ITU documents, as identified in this clause, are valid within the context of this International Standard. The reference to such a specification within this International Standard does not give it any further status within ISO/IEC. In particular, it does not give the referenced specification the status of an International Standard.

ISO/IEC 14776-362, Information technology – Small Computer System Interface (SCSI) – Part 362: Multimedia commands-2 (MMC-2) [ANSI INCITS 333-2000]

PC Card Standard, February 1995, PCMCIA 1

CompactFlash™ Association Specification, Revision 1.42

<sup>&</sup>lt;sup>1</sup> For the PC Card Standard published by the Personal Computer Memory Card International Association, contact PCMCIA at 408-433-2273 or http://www.pcmcia.org.

For the Compact Flash Association Specification published by the Compact Flash Association, contact the Compact Flash Association at <a href="http://www.compactflash.org">http://www.compactflash.org</a>.

CompactFlash™ is the trademark of the Compact Flash Association. This information is given for the convenience of users of this document and does not constitute an endorsement by IEC or ISO of this trademark. Equivalent descriptons may be used if they can be shown to lead to the same results.